# Design of Low power, Low Jitter Ring Oscillator Using 50nm CMOS Technology

Nidhi Thakur

Abstract A modified ring oscillator presented in this paper. The voltage control oscillator is designed and simulated in 50nm CMOS technology. The frequency of oscillation of the VCO is 2.6GHz with 0.064 mW power dissipation and the center drain current of 64uA is used. Tuning range is of 72% and the jitter is of 39.8pS.

•

Index Terms Voltage Controlled Oscillator (VCO), power dissipation, jitter, tuning range, phase locked loop (PLL)

# **1 INTRODUCTION**

Wireless and Wire line communication systems such as wireless Local Area Network, Mobile and Satellite communication, backplane interconnects and chip-to-chip communication systems, clock generation and skew compensation in microprocessors and other communication devices are widely used Phase Locked Loop(PLL) as a basic building block[3]. The VCO jitter performance in these applications can impact the output clock's timing jitter which often limits the system performance [9] .Also in most of the narrow band communication systems the frequency synthesizer plays a major role in generating local oscillation signal or carriers and is usually implemented through a PLL[5]. The high power consumption in the frequency synthesizer is mainly due to the VCO therefore one of the most challenging building block of the PLL is the VCO .Among many other oscillator topologies the ring oscillator is attractive for its high frequency, wide range of operation and small die size. A ring oscillator consists of multiple stages of delay cells. Delay cell can be design with differential pair and CMOS inverter. In this paper CMOS inverter is used as a delay cell [7].

## 2 VCO Design

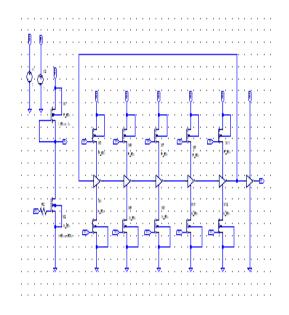

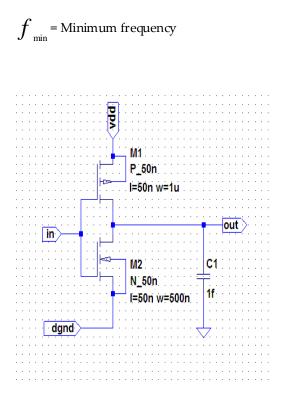

VCO is a frequency modulated oscillator whose instantaneous output frequency is directly proportional to its control voltage .A ring oscillator can be smoothly integrated in a standard CMOS process without taking extra processing steps because it does not require any passive resonant element compare to CMOS LC-tank oscillator [6], [7], [8].In this work 5-stage CMOS inverter forms a closed path with positive feedback [10]. The schematic of the whole VCO is shown in fig 1.Voltage control oscillator have a CMOS inverter circuit as shown in figure2.This inverter circuit is connected to current sources M3 and M4 that limit the current available to the inverter. The currents in MOSFETs M1 and M2 are mirrored in each inverter stage.

## 2.1 Oscillation frequency

The oscillation frequency is given by -

$$f_{osc} = \frac{I_d}{NC_{tot} \cdot V_{DD}}$$

(1)

Where,

N= Number of stages

$$I_d = I_{d3} = I_{d4}$$

= center drain current

Nidhi Thakur is currently pursuing masters degree program in Microelectronics and VLSI engineering in RGPV University, Bhopal, India. E-mail:nidhi.thkr63@gmail.com.

International Journal of Scientific & Engineering Research Volume 3, Issue 3, March-2012 ISSN 2229-5518

$$C_{tot} = C_{out} + C_{in}$$

(2)

$$C_{tot} = C_{ox}^{\prime} (W_p \cdot L_p + W_n \cdot L_n)$$

(3)

$$\boldsymbol{C}_{in} = \frac{3}{2} \boldsymbol{C}_{ox}^{\prime} (\boldsymbol{W}_{p} \cdot \boldsymbol{L}_{p} + \boldsymbol{W}_{n} \cdot \boldsymbol{L}_{n})$$

(4)

$$C_{tot} = \frac{5}{2} C_{ox} (W_{p} L_{p} W_{n} L_{n})$$

(5)

Figure 1 Schematic view of VCO

## 2.2 Tuning range

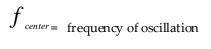

VCO designed such that its oscillation frequency is controlled by input voltage. For communication it is important to have a large tuning range among the other structure of VCO ring oscillator has a large tuning range [4].Tuning range is shown in fig 3. Tuning range can be defined as-

Tuning range% =

$$\frac{f_{\text{max}} - f_{\text{min}}}{f_{center}} \times 100$$

(6)

Where

$$f_{center} = f_{osc}$$

= frequency of oscillation

$f_{\rm max}$  = Maximum frequency

Figure 2 Schematic view of CMOS inverter

# 2.3 Gain

Gain of the VCO is the slope of the curves given in fig3.It is defined as

$$K_{VCO} = 2 \prod \left( \frac{f_{\text{max}} - f_{\text{min}}}{V_{\text{max}} - V_{\text{min}}} \right) \text{ radian/v.s}$$

(7)

# 2.4 JITTER

It is the interval between two times of maximum effect (or minimum effect) of a signal property that varies regularly with time. It is defined as-

$$\frac{\Delta t_{jitter}}{f_{center}} = \frac{1}{f_{center}} - \frac{1}{f_{center} + \Delta f_{VCO}}$$

(8)

IJSER © 2012 http://www.ijser.org 2

Figure3: graphical representation of frequency vs. voltage

## 2.5 Power dissipation

The average power dissipated by the VCO is given as [11]-

$$I_{avg} = N.V_{DD}C_{tot} f_{osc}$$

(9)

$$p_{avg} = V_{DD} \cdot I_{avg}$$

(10)

$$\boldsymbol{I}_{avg} = \boldsymbol{I}_{d} \tag{11}$$

$$p_{avg} = V_{DD} \cdot I_d \tag{12}$$

## **3 EXPERIMENTAL RESULTS**

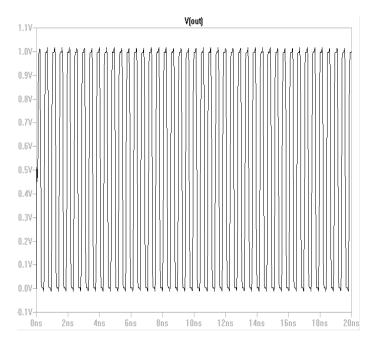

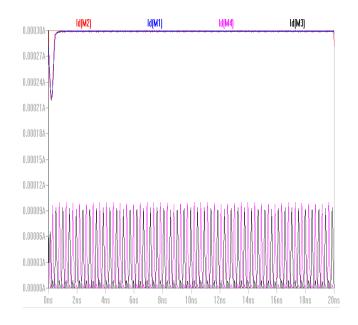

The ring oscillator for this work has been realized in 50nm CMOS technology. The output frequency can vary from 0.7GHz to 2.56GHz, the tuning range is found to be 72%

which is much better than what is reported earlier. At 2.56 GHz the average power consumption is 0.064mW at 1V supply voltage which is also much lesser compared to

65nm and 180nm designs. The jitter for the circuit is 39.8pS. The performance result of the Voltage control oscillator compared with earlier work is summarized in Table 1.

Figure 4 Simulation result of output voltage vs. time

Figure 5 Simulation result of drain current

Table1. Comparison with state of art

IJSER © 2012 http://www.ijser.org International Journal of Scientific & Engineering Research Volume 3, Issue 3, March-2012 ISSN 2229-5518

|                     |       | 1      | · · · · · · · · · · · · · · · · · · · |

|---------------------|-------|--------|---------------------------------------|

| Work                | [2]   | [1]    | This<br>work                          |

| Max. frequency(Hz)  | 5.89G | 800M   | 2.56G                                 |

| LC/Ring             | LC    | Ring   | Ring                                  |

|                     | 4.65- |        |                                       |

| Frequency range(Hz) | 5.89G | 2-40M  | 0.7-2.56G                             |

| Operating voltage   | 1.3V  | 1.8V   | 1V                                    |

| Technology          | 65nm  | 0.18um | 50nm                                  |

| Power consumption   | 4.8mW | 3mW    | 0.064mW                               |

| Tuning range        | -     | 24%    | 72%                                   |

| No. of stages       | -     | 1      | 5                                     |

| Jitter              | -     | -      | 39.8pS                                |

# **4 CONCLUSION**

The design presented in a 50nm CMOS technology and is designed using CMOS inverter with current mirror .The Voltage control oscillator consumes power around 0.064mW for 1V supply and the tuning range is 72%.

## REFRENCES

- Mike Shuo-Wei Chen et al, "A Calibration-Free 800MHz Fractional-N Digital PLL with Embedded TDC", ISSCC, February 2010.

- [2] Mostafa Savedi Oskooei, AliAfzali-Kusha, S.M Atarodi. "A High-Speed and Low-Power Voltage Controlled Oscillator in 0.18-um CMOS Process", *IEEE Journal of Solid-State Circuits*, pp.933-936, 2007.

- [3] Neda Nouri and Shahriar Mirabbasi, "A900MHZ-2GHZ LOW-SWING LOW-POW ER 0.18μM CMOS PLL", IEEE CCECE/CCGEI, Saskatoon, 0-7803-8886-0, pp.1558-1561, May 2005.

- [4] Lizhong Sun and Tadeusz A. Kwasniewski, "A 1.25-GHz 0.35-um Monolithic CMOS PLL Based on a Multiphase Ring Oscillator", *IEEE Journal of Solid-State Circuits*, pp.910-916, VOL. 36, JUNE 2001.

- [5] M.Vamshi Krishna, J.Xie, M.A.Do, C.C.Boon, K.S.Yeo and Aaron, A 1.8-V 3.6-mW 2.4-GHz Fully integrated CMOS Frequency Synthesizer for *IEEE* 802.15.4, 18th IEEE/IFIP International Conference on VLSI and System-on-Chip ,978-1-4244-6471, pp.387-391, May 2010.

- [6] Mehdi Ayat ,Behnam Babaei , Reza Ebrahimi Atani , Sattar Mirzakuchaki and Babak Zamanlooy, "Design of A 100MHz - 1.66GHz, 0.13µm CMOS Phase Locked Loop", International Conference on Electronic Devices, Systems and Applications, 978-1-4244-6632-0, pp.154-158,2010.

- [7] S. J. Lee, B. Kim, and K. Lee, "A novel high-speed ring oscillator for multiphase clock generation using negative skewed delay scheme," *IEEE Journal of Solid-State Circuits, pp. 289–291, vol. 32,* Feb-1997.

- [8] C. H. Park and B. Kim, "A Low-Noise 900 MHz VCO in 0.6 μm CMOS," *IEEE Journal of Solid State Circuits*, pp. 586 – 591, 1999.

- [9] Ali Hajimiri, Sotirios Limotyrakis, and Thomas H. Lee, "Jitter and Phase Noise in Ring Oscillators", *IEEE Journal of Solid-State Circuits*, 0018–9200/99, pp.790-804,VOL. 34, JUNE 1999.

- [10] B. Razavi, "Design of Integrated Circuits for Optical Communications", McGraw-Hill, New York, 2003.

- [11] Ashish Raman and R. K. Sarin , "0.18-μm Low Power CMOS Ring Oscillator for Radio Frequency Applications", *International Journal of Computer Theory and Engineering*, pp.770-774, Vol. 3, December 2011.

4

International Journal of Scientific & Engineering Research Volume 3, Issue 3, March-2012 ISSN 2229-5518

IJSER © 2012 http://www.ijser.org